在人类历史的大部分时间里,我们依靠天文计时来计划我们的生活。现在我们拥有复杂的时钟,可以帮助我们管理日常生活。随着现代生活变得越来越疯狂,我们需要追踪到几分之一秒,而集成电路PCB板上的晶体振荡器合理布局或许可能实现。

通常,在PCB上的电阻和电容不会随着时间的推移保持恒定,它们会随着电路板的温度而变化,组件也会随着老化而退化,这些因素会导致时钟频率随时间漂移。

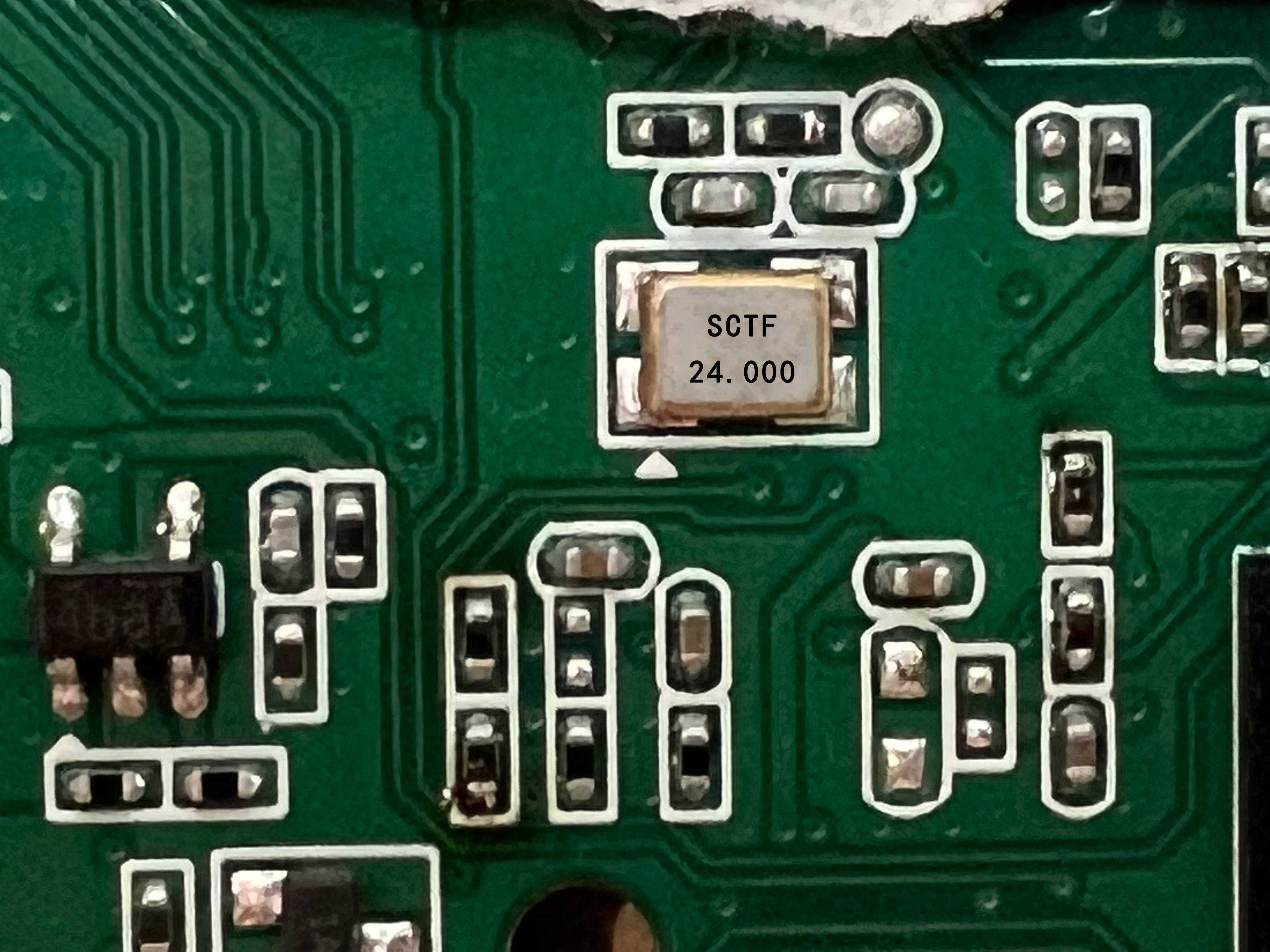

如果频率稳定特性和精度至关重要,选用晶体振荡器是更好的选择。切割成特定形状的石英晶体可以以特定的共振频率振动,并且该频率对温度变化高度稳定。如果正确放置和连接到您的集成PCB电路板中,晶体振荡器可以输出从 kHz 到 MHz 的稳定频率。

任何使用时钟数字系统都存在设计挑战。在 PCB 中寄生电容和信号反射等问题会降低信号完整性。其中一些设计问题在高频下变得更加紧迫。幸运的是,有一些设计策略将有助于在您的设计中保持信号完整性。

1. 最小化传播延迟和时钟偏移

逻辑电路中的切换,特别是 TTL 和 CMOS 逻辑器件中的切换,会导致传播延迟在时钟输出的下游累积。虽然这往往是纳级,但它与高频电路中时钟脉冲的宽度相当。

无论器件中使用何种时钟,都可能发生时钟偏移。随着时钟信号被路由到各种电子元件,走线长度的变化会导致时间延迟。当时钟偏斜与传播延迟相结合时,并行走线中时钟脉冲之间的不匹配可能会很严重。

时钟偏移和传播延迟可以通过调整信号走线的长度来补偿。应使连续组件之间的差分走线长度相等,以最大限度地减少时钟偏移。某些并行走线可能包含不同数量的组件,在印刷电路板上放置走线时应考虑每个组件的传播延迟。

2. 地平面放置

一些 PCB 设计人员可能倾向于直接在其接地层上运行他们的电源和信号走线。不建议这样做,因为不正确的接地层放置会导致您的时钟电路充当天线。该电路不仅容易受到外部 EMI的影响,而且该电路还会产生射频辐射,从而在附近的其他电路中引起 EMI。

对于特定的时钟频率,接地层的厚度仅为 1/2 波长。由于晶体振荡器是一个真正的宽带电流源,时钟信号及其返回电流都包含一个高频分量。如果允许这些电流流过接地平面,您就创建了一个中心馈电贴片天线。

如果时钟信号频带与接地层谐振频率之一重叠,则可以在接地层中产生强电流。但是,如果将电源层和接地层分开,则高频电流环路引起的辐射会减少。这也将降低对外部 EMI 的敏感性。

3. 精准匹配电容

晶体的信号完整性可以通过晶振两端的电容来保持。一个应该连接在高压引脚和接地层之间,另一个连接在接地引脚和接地层之间。您需要将电容与您选择的特定晶体相匹配。即使在同一制造商内,不同的晶体的型号所需的电容也会有所不同。

您的晶体电路中将包含一个负载电容规格(通常为 20 到 50 pF),您可以使用它来确定与您的晶体一起使用的电容。每个电容应该是负载电容值的两倍,减去任何杂散电容。杂散电容值往往是几个 pF。当您在时钟信号走线和板上的其他 IC 之间建立连接时,不要忘记晶振两端的电容。

4. 避免时钟信号线过孔

过孔可以充当迹线中的电容或电感不连续性。这意味着承载时钟信号的走线可能会从通孔反射并导致信号完整性问题。如果可能,建议不要通过孔路由晶体振荡器产生的较高频率的信号。如果必须使用通孔以保持外形尺寸,则迹线和通孔必须阻抗匹配以防止反射。

过孔和走线之间的阻抗匹配可以通过最小化或消除过孔中的短截线来完成。未使用的短截线就像一条未端接的传输线,在其谐振频率附近有明显的信号衰减,通常没有任何用处,可以通过背钻去除。然而,背钻需要额外的制造步骤并且会增加制造成本。